DSP Group selected the DesignWare ARC EM5D processor from Synopsys for its combined high-efficiency control and signal processing capabilities. DSP Group's DBMC2-TWS integrates powerful hybrid ANC processing with advanced audio features in a single, compact, low-power device, while the scalable family of DSP-enhanced ARC EM processors can be tailored for the optimal balance of performance and power consumption.

The processing capabilities of the ARC EM5D enable the deployment of advanced sound processing features, such as adaptive active noise cancellation (ANC), user ear placement characterization, and smart ambient awareness control. This allows the headset to autonomously respond to changes in product fit or the ambient sound conditions. DSP Group also leveraged the DesignWare ARC MetaWare Development Toolkit to ease digital signal processing (DSP) software development for its audio and voice processing SoC.

"DSP Group is dedicated to the design of SoCs and supporting algorithms that enable the unification of voice, audio, video, and data connectivity for mobile, enterprise, consumer, and IoT devices," says Dotan Sokolov, CVP, Head of R&D at DSP Group. "In the case of our DBMC2-TWS solution, the scalability and efficiency of Synopsys' DSP-enhanced ARC EM processors give us the flexibility to meet extreme power, size, and performance demands, while also providing the cutting-edge features and capabilities required to stay ahead of the competition in an exciting hearables market that is expanding rapidly."

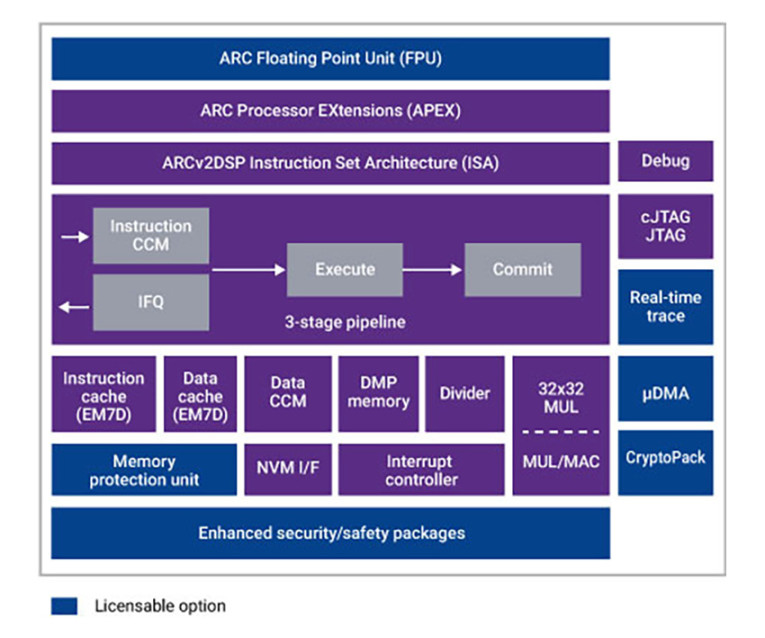

The DSP-enhanced ARC EM processor family, which includes the EM5D, EM7D, EM9D, and EM11D processors, implements a scalable pipeline that offers an optimal balance of performance, power consumption and size for a range of control and DSP applications. Like all ARC processors, the DSP-enhanced EM processors are highly configurable so that each instance can be tailored to achieve the optimum balance of DSP and RISC performance. ARC Processor EXtension (APEX) technology offers designers the ability to create user-defined instructions, enabling the integration of custom hardware accelerators that improve application-specific performance while reducing power consumption and memory footprint.

The DSP-enhanced ARC EM processors are supported by the DesignWare ARC MetaWare Development Toolkit, a complete suite of tools for developing, debugging and optimizing software targeted for ARC processors, which includes an enhanced C/C++ compiler supporting the 150+DSP instructions available for efficient algorithm development.

"Next-generation voice and audio processing applications require the lowest power consumption to be competitive in the market," says John Koeter, senior vice president of marketing and strategy for IP at Synopsys. "Synopsys' DSP-enhanced DesignWare ARC EM Processors deliver highly efficient processing with increased bandwidth for control and DSP tasks, enabling companies like DSP Group to extend the battery life and deliver differentiated functionality in their products."

www.dspg.com

www.synopsys.com/designware