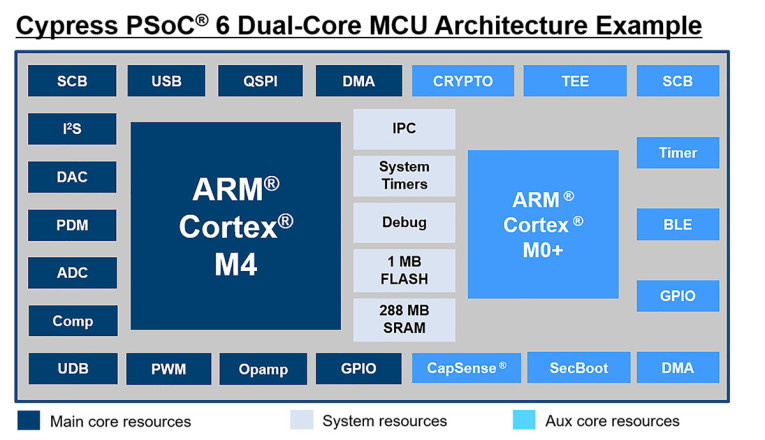

The dual-core ARM Cortex-M4 and Cortex-M0+ architecture lets designers optimize for power and performance simultaneously. PSoC 6 enables engineers to create innovative, next-generation IoT devices leveraging the PSoC fabric with its easy-to-use, software-defined peripherals. The architecture offers flexible wireless connectivity options, including fully integrated Bluetooth Low Energy (BLE) 5.0.

"As the leader in wireless solutions for the IoT, we saw first-hand that our customers need a better processing solution that balances performance and power, while implementing critical security functions for connected devices," says Hassane El-Khoury, President and CEO at Cypress. "Our PSoC 6 MCU architecture is purpose-built to solve these problems, marking a significant addition to our broad embedded systems solution portfolio for the IoT."

Cypress' proprietary ultra-low-power 40-nm SONOS process technology enables the PSoC 6 MCU architecture to feature industry-leading power consumption with 22 µA/MHz and 15 µA/MHz of active power on the ARM Cortex-M4 and Cortex-M0+ cores, respectively. With dynamic voltage and frequency scaling (DVFS), the PSoC 6 MCU architecture offers both performance- and power-critical processing capability. The dual-core architecture enables power-optimized system design where the auxiliary core can be used as an offload engine for power efficiency, allowing the main core to sleep.

The PSoC 6 MCU architecture provides a hardware-based Trusted Execution Environment (TEE) with secure boot capability and integrated secure data storage to protect firmware, applications and secure assets such as cryptographic keys. PSoC 6 implements a broad set of industry-standard symmetric and asymmetric cryptographic algorithms, including Elliptical-Curve Cryptography (ECC), Advanced Encryption Standard (AES), and Secure Hash Algorithms (SHA 1,2,3) in an integrated hardware coprocessor designed to offload compute-intensive tasks. The architecture supports multiple, simultaneous secure environments without the need for external memories or secure elements, and offers scalable secure memory for multiple, independent user-defined security policies.

"Every connected device represents a potential network vulnerability. With billions of potential vulnerabilities, security is paramount and the need to design in security at the lowest level in an IoT device is more important than ever," says John Weil, vice president of the MCU Business Unit at Cypress. "We built PSoC 6 to enable our customers to protect their products from cyber-attacks while at the same time empowering them to create new, innovative IoT devices leveraging the flexible and easy-to-use PSoC architecture."

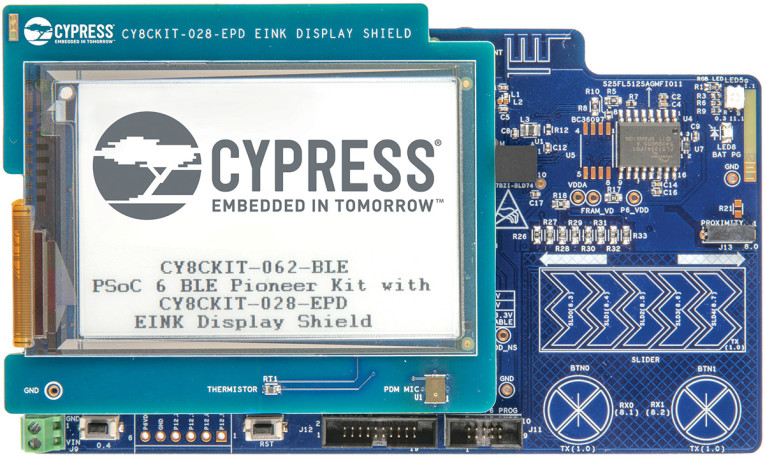

Software-defined peripherals can be used to create custom analog front-ends (AFEs) or digital interfaces for innovative system components such as electronic-ink displays. The PSoC 6 MCU architecture features the latest generation of Cypress' CapSense capacitive-sensing technology, enabling modern touch and gesture-based interfaces that are robust and reliable. The architecture is supported by Cypress' PSoC Creator Integrated Design Environment (IDE) and the expansive ARM ecosystem.

PSoC 6 silicon, kits and software are currently sampling. Full production is expected early in the fourth quarter of 2017.

www.cypress.com/PSoC6